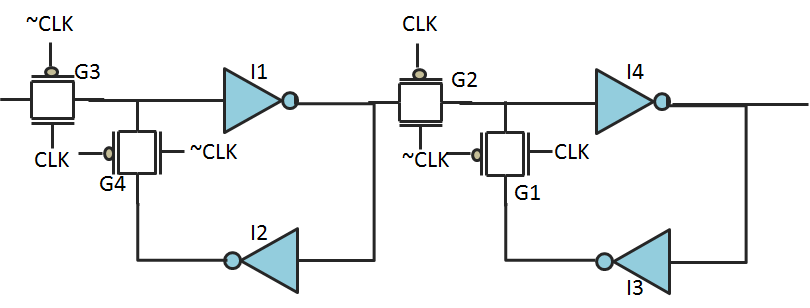

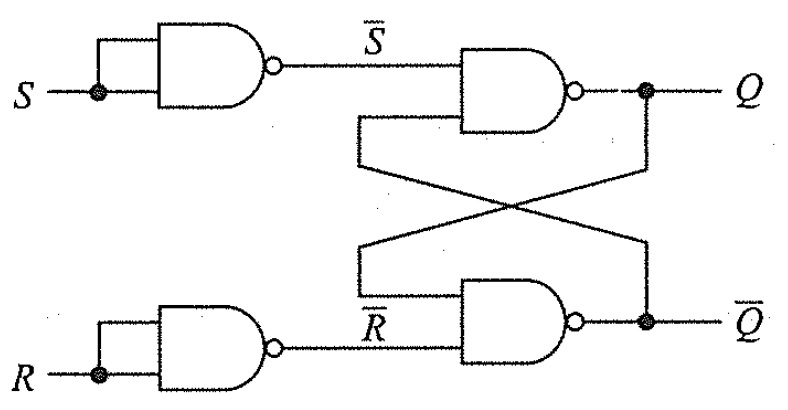

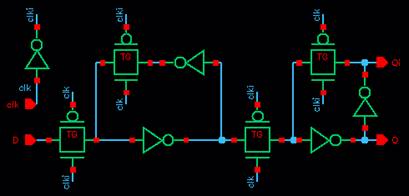

Three different flip-flop architectures. Dynamic MSFFs: (a)TG-MSFF and... | Download Scientific Diagram

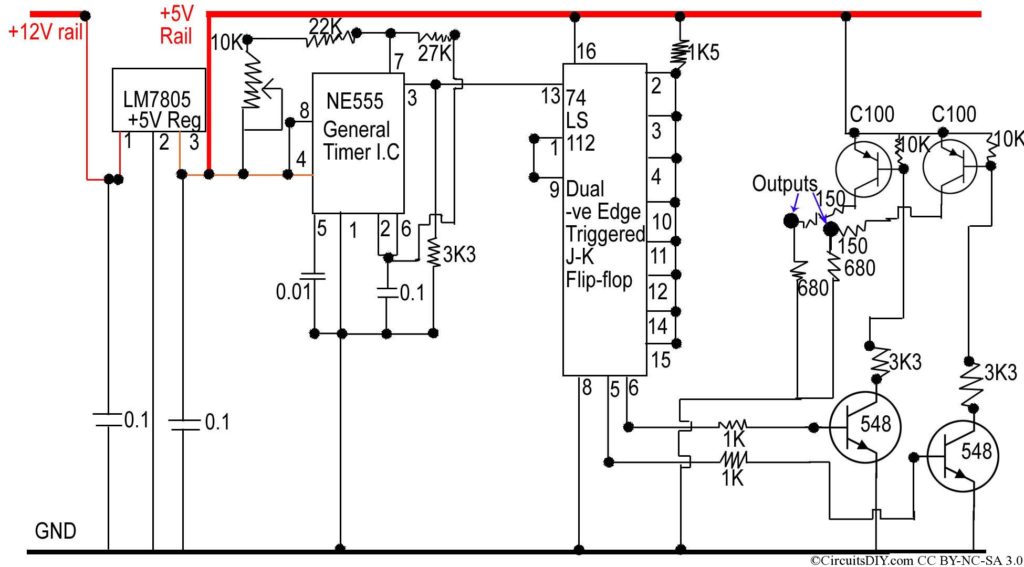

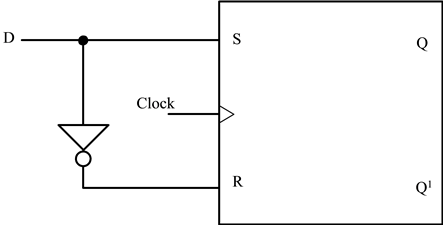

Figure 9 | A Modified Implementation of Tristate Inverter Based Static Master-Slave Flip-Flop with Improved Power-Delay-Area Product

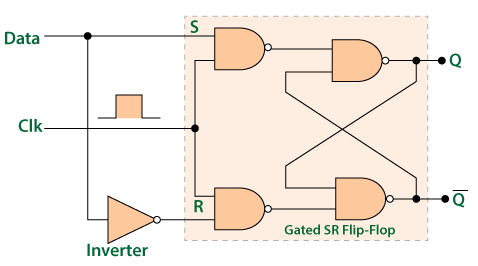

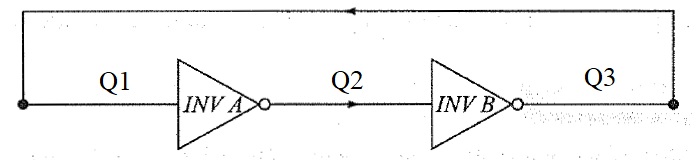

A Modified Implementation of Tristate Inverter Based Static Master-Slave Flip-Flop with Improved Power-Delay-Area Product

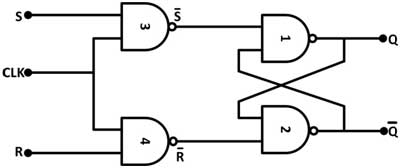

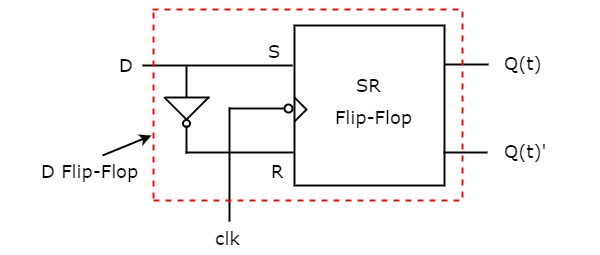

Figure 5 | A Modified Implementation of Tristate Inverter Based Static Master-Slave Flip-Flop with Improved Power-Delay-Area Product